硬件基础知识

计算机的基本硬件系统由 运算器、控制器、存储器、输入设备和输出设备5大部分组成。

CPU

运算器和控制器等部件被集成在一起,统称为中央处理单元(Central Processing Unit),即CPU。

具体包括 运算器、控制器、寄存器、内部总线。

CPU的功能:

CPU是硬件系统的核心,主要是数据的加工处理,能完成算术运算、逻辑运算和控制功能。

具体即:

- 程序控制:按照程序的安排来执行指令。

- 操作控制:产生每条指令的操作信号,将操作信号送往不同部件,控制相应部件按指令要求操作。

- 时间控制:对每条指令的执行时间进行控制。

- 数据处理:对数据进行算术运算、逻辑运算等。

- 异常控制:对系统内部和外部的中断(异常)做出相应,进行处理。

中央处理器的功效主要为处理指令、执行操作、控制时间、处理数据。

---- 百科

运算器

运算器是执行部件。接收控制器的命令,根据控制器发出的控制信号进行操作。

运算器的功能:

- 算术运算,如加减乘除,及附加运算。

- 逻辑运算,并进行逻辑测试,如与、或、非、零值测试和等值比较。

具体部件 ⚡️ 💯

1️⃣ 算法逻辑单元ALU

进行算术运算和逻辑运算。

2️⃣ 累加寄存器AC

为ALU提供工作区,专门存放算术或逻辑运算的一个操作数和运算结果,即暂时存放ALU运算的结果信息。

3️⃣ 数据缓冲寄存器DR

暂时存放由内存储器读写的一条指令或一个数据字。相当于CPU和内存及外围设备的中转站。在单累加器结构的运算器中,数据缓冲寄存器还可兼作为操作数寄存器。

4️⃣ 状态条件寄存器PSW

保存各种条件码内容,主要分为状态标志和控制标志。

::: tip 累加寄存器(AC)通常简称为累加器,它是一个通用寄存器。 运算器中至少要有一个累加寄存器。 :::

::: tip ALU: Arithmetic and Logic Unit,

AC: Accumulator

DR: Data Register,

PSW: Program Status Word :::

控制器

用于控制整个CPU的工作。控制器不仅要保证程序的正确执行,而且要能够处理异常。一般包括指令控制逻辑、时序控制逻辑、总线控制逻辑和中断控制逻辑。

其主要部件有 ⚡️ 💯

1️⃣ 指令寄存器IR

当CPU执行一条指令时,先从内存储器取到缓冲寄存器中,再送于指令寄存器中暂存,再有指令译码器根据指令寄存器的内容产生各种操作。

2️⃣ 程序计数器PC(Program Counter)

又称指令计数器,用来存放当前欲执行指令(下一条)的地址。注意是地址。它与主存的MAR之间有一条直接通路,且具有自加1的功能,即可形成下一条指令的地址, 即用于存放下一条指令所在单元的地址的地方。。

3️⃣ 地址寄存器AR

用来保存当前CPU所要访问的内存单元或I/O设备的地址。

由于内存和CPU之间存在着速度上的差别,所以必须使用地址寄存器来保存地址信息,直到内存读/写操作完成为止。

4️⃣ 指令译码器ID

指令包括操作码和地址码两部分。指令译码器就是对指令中的操作码字段进行分析解释,识别指令规定的操作,并发出具体控制信号

指令寄存器IR

An instruction register holds a machine instruction that is currently being executed. In general, a register sits at the top of the memory hierarchy. A variety of registers serve different functions in a central processing unit (CPU) – the function of the instruction register is to hold that currently queued instruction for use.

用于暂存当前正在执行的指令。

寄存器组

分为专用寄存器和通用寄存器。 运算器和控制器中的寄存器是专用寄存器,其作用是固定的。

多核CPU

CPU的核心又称为内核,是由单晶硅以一定工艺制造出来的。

CPU所有的计算、接收/存储命令、处理数据都是由核心执行。

所谓多核心,即在一个单芯片上面集成2个甚至多个处理器内核,并且每个处理器内核都有自己的逻辑单元、控制单元、中断处理器、运算单元、一级Cache、二级Cache等。

多核CPU系统的最大的优点是可以满足用户同时进行多任务处理。理论上,在任何时间内每个内核分别执行各自的任务,不存在交替的问题。

存储器

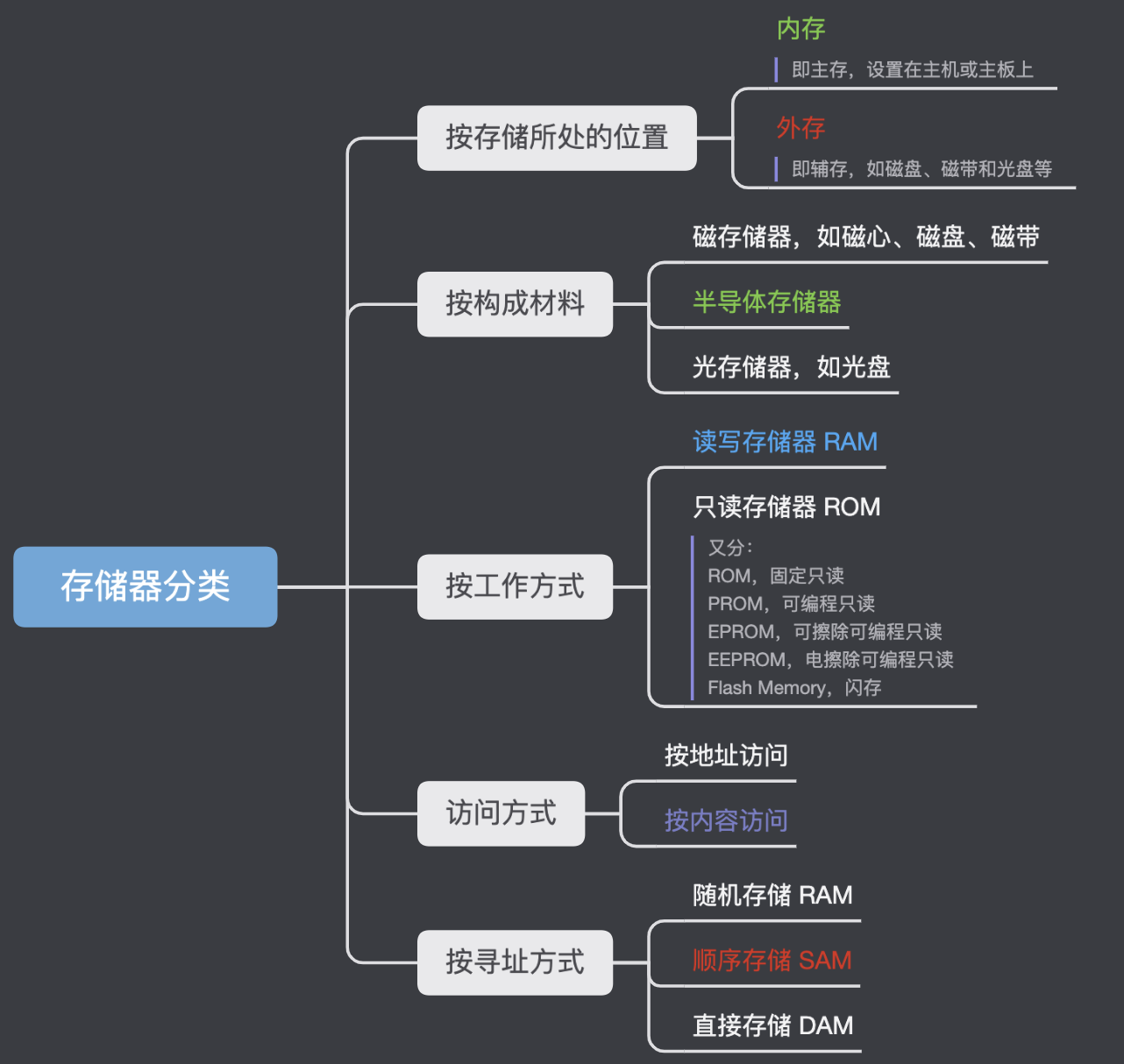

分类

随机访问存储器

随机访问存储器RAM,分为静态RAM(SRAM)和动态RAM(DRAM)两类。

静态的更贵,也更快。

外存储器

主要是磁盘、磁带、光盘。

CPU不能直接访问外存储器中的内容,只有将其以文件为单位调入主存后才可访问。

总线

所谓总线(Bus),是指计算机和设备之间传输信息的公共数据通道。

总线分类

微机中的总线分为:数据总线、地址总线、控制总线3类。

1️⃣数据总线

Data Bus = DB, 用来传输数据信息,是双向的。

CPU即可通过DB从内存或输入设备读入数据,也可以通过DB将内部数据送至内存或输出设备。

DB的宽度决定了CPU和计算机其他设备之间每次交换数据的位数。

2️⃣地址总线

Address Bus = AB,用于传送CPU发出的地址信息,是单向的。

存储器是按地址访问的,每个存储单元都有一个固定地址。

由于地址只能从CPU传向外部存储器或I/O端口,所以地址总线总是单向三态的,这与数据总线不同。

地址总线的位数决定了CPU可直接寻址的内存空间大小,比如8位微机的地址总线为16位,则其最大可寻址空间为2<sup>16</sup>=64KB,16位微型机的地址总线为20位,其可寻址空间为2<sup>20</sup>=1MB。

一般来说,若地址总线为n位,则可寻址空间为2<sup>n</sup>字节。 💯 注意单位是字节

3️⃣控制总线

Controll Bus = CB, 用来传送控制信号、时序信号和状态信息等。

控制总线的传送方向由具体控制信号而定,一般是双向的。

常见的总线

- ISA总线,即工业标准总线,只支持16位的I/O设备。

- EISA总线,32位总线。

- PCI总线,32位或64位

- PCI Express 总线,简称PCI-E

- 前端总线,Front Side Bus = FSB,是将CPU连接到北桥芯片的总线。

- RS-232C总线。

- SCSI总线

- SATA, 主板和存储设备之间传输数据

- USB, 目前常用的为USB3.0, 支持5Gb/s的传输速率,支持即插即用。

- IEEE1394总线

- IEEE-488总线

输入输出控制

I/O设备

分为块设备和字符设备。

- 块设备:把信息放在固定大小的块中,每个块都应自己的地址,可寻址。例如磁盘、USB闪存、CD-ROM等

- 字符设备:以字符为单位接收或发送一个字符流,不可寻址。如打印机、网卡、鼠标键盘。

I/O 设备一般都包含设备控制器,一般以芯片的形式出现,如南桥芯片。其中包含了硬盘控制器、USB控制器、网卡、声卡等。

程序控制方式

程序控制I/O是指外设数据的输入/输出过程是在CPU执行程序的控制下完成的。

这种方式分为:无条件传送和程序查询两种情况。

无条件传送,是指外设总是准备好的,可以无条件地随时接收CPU发来得输出数据。

中断方式

在中断方式下,I/O设备工作时CPU不再等待,而是进行其他的操作,当I/O设备完成后,通过一个硬件中断信号通知CPU,CPU再来处理接下来的工作。

和程序控制方式相比,中断方式因为CPU无须等待而提高了效率。

DMA方式

DMA = Direct Memory Access,直接内存读取。是指数据在内存和I/O设备间的直接成块传送,即不需要CPU的干涉。

输入输出处理IOP

通道是一个具有特殊功能的处理器,又称为输入输出处理器(Input/Output Processor,IOP)。

通道分担了CPU的一部分功能,可以实现对外围设备的统一管理,完成外围设备和主存之间的数据传送。

⭐️本章相关真题及解析

2014第1题:考察CPU

在CPU中,常用来为ALU执行算术逻辑运算提供数据暂存运算结果的寄存器是:累加寄存器。

解析:

ALU: Arithmetic Logic Unit,算术逻辑单元。

ALU是计算机的数学大脑,理解了ALU的设计和功能后,你就理解了现代计算机的基石。

ALU就是计算机中负责运算的组件,基本上其他组件都需要用到它。

ALU有两个单元,1个算术单元,1个逻辑单元。

ALU架构:

ALU可以直接访问处理器控制单元,主存储器以及输入和输出设备的输入和输出。

输入和输出数据通过称为总线的电子路径传输。

输入对应于一条指令,该指令包括一个或多个操作数,一个操作代码,在某些情况下还包括格式代码。

累加器是一个数据寄存器,在运算过程中暂时存放操作数和中间运算结果,不能长时间保存一个数据。

记住,是暂时存放,因此也称累加暂存器

如果没有像累加器这样的寄存器,那么在每次计算 (加法,乘法,移位等等) 后就必须要把结果写回到 内存,也许马上就得读回来。

然而存取主存的速度是比从算术逻辑单元到有直接路径的累加器存取更慢。

::: tip

也就是说获得数据的速度: 寄存器>主存>硬盘

存储数据的量: 寄存器<主存<硬盘

:::

2015年第2题

计算机中CPU对其访问速度最快的是(2)。

A.内存 B.Cache C.通用寄存器 D.硬盘

【答案】C

速度: 通用寄存器 > Cache > 内存/主存 > 外存/磁盘

2015年第3题

Cache的地址映像方式中,发生块冲突次数最小的是____。

A.全相联映像 B.组相联映像 C.直接映像 D.无法确定的

【答案】A

Cache工作时,需要拷贝主存信息到Cache中,就需要建立主存地址和Cache地址的映射关系。

Cache的地址映射方法主要有三种,即全相联影像、直接映像和组相联映像。

- 全相联方式: 主存的任意一块可以映像到Cache中的任意一块,其特点是块冲突概率低,Cache空间利用率高,但是相联目录表容量大导致成本高、查表速度慢;

- 直接映像方式: 是指主存的每一块只能映像到Cache的一个特定的块中,整个Cache地址与主存地址的低位部分完全相同,其特点是硬件简单,不需要相联存储器,访问速度快(无需地址变换),但是Cache块冲突概率高导致Cache空间利用率很低;

- 组相联方式: 是对上述两种方式的折中处理,对Cache分组,实现组间直接映射,组内全相联,从而获得较低的块冲突概率、较高的块利用率,同时得到较快的速度和较低的成本。

2015年4题

计算机中CPU的中断响应时间指的是(4)的时间。

A.从发出中断请求到中断处理结束

B.从中断处理开始到中断处理结束

C. CPU分析判断中断请求

D.从发出中断请求到开始进入中断处理程序

【答案】D

中断系统是计算机实现中断功能的软硬件总称。

一般在CPL中设置中断机构,在外设接口中设置中断控制器,在软件上设置相应的中断服务程序。

中断源在需要得到CPU服务时,请求CPU暂停现行工作转向为中断源服务,服务完成后,再让CPU回到原工作状态继续完成被打断的工作。

中断的发生起始于中断源发出中断请求,中断处理过程中,中断系统需要解决一系列问题,包括中断响应的条件和时机,断点信息的保护与恢复,中断服务程序入口、中断处理等。

中断响应时间,是指从发出中断请求到开始进入中断服务程序所需的时间。

2015年5题

总线宽度为32bit,时钟频率为200MHz,若总线上每5个时钟周期传送一个32bit的字,则该总线的带宽为(5)MB/S。

A.40 B.80 C.160 D.200

【答案】C

总线宽度是指总线的位数,即数据信号的并行传输能力,也体现总线占用的物理空间和成本;

总线的带宽是指总线的最大数据传输率,即每秒传输的数据总量。

总线宽度与时钟频率共同决定了总线的带宽。

总线上每5个时钟周期传送一个32bit的字,我们将32bit单位转换成4byte

可以算出每个时钟传送=200/5=40Hz

所以总线的带宽是40*4=160MB/S

32bit/8=4Byte,200MHz/5×4Byte=160MB/s

⭐️ 补充知识点

频率是单位时间内完成周期性变化的次数, 是描述周期运动频繁程度的量. 常用符号f或ν表示,单位为秒分之一。

(为了纪念德国物理学家赫兹的贡献,单位赫兹Hz)

⚡️ 周期和频率的关系

二者的关系:f=1/T,二者成反比(其中f为频率,T为周期)。

频率是单位时间内完成周期性变化的次数,是描述周期运动频繁程度的量。

周期,物体作往复运动或物理量作周而复始的变化时,重复一次所经历的时间。

⚡️ 时钟频率: 就是单位时间内脉冲个数, 即每秒逻辑零状态与逻辑一状态来回切换次数(周期性变化)。